# LC-007

# 多目的分散 GA をベースとしたパフォーマンスドリブン配置手法 Performance Driven Placement based on Distributed Genetic Algorithm

吉川 雅弥<sup>†</sup> Masaya Yoshikawa

# 1. はじめに

デシミクロンオーダーのVLSI設計では,タイミング・消費電力・配線混雑などをトータルで最適化するフィジカルデザイン手法が求められる。タイミングや消費電力を最適化するためにレイアウト結果を修正する方法がこれまで一般的にとられているが,SIAロードマップでも指摘されているように, $0.1\mu$  m以下のプロセスではこのような修正箇所は数千箇所を越え,後処理でのレイアウト修正は限界を超えることが予想される。そこで本稿では,基本アルゴリズムに遺伝的アルゴリズム(GA)<sup>(1)</sup>を採用し,消費電力やタイミング制約を同時に最適化する配置手法を提案する。GAをレイアウト問題に適用した報告は文献(2)~(5)の他にいくつかあるが,ベクトルランキング法をベースとした多目的分散GA配置とそれを並列計算機に実装し,その効果を実証した発表はこれまでみあたらない。

# 2. 配置アルゴリズム

提案する配置手法は,多段分割を行う概略配置と分割領域内での配置を行う詳細配置の2ステップで構成した。

## 2.1 選択オペレーション

本研究では,以下に示す5つの評価関数を導入した。

- (1)チップ面積による評価

- (2)配線混雑による評価

- (3)タイミング制約による評価

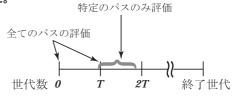

タイミング制約を満足するためには,すべてのパスディレイが 1 クロックサイクル以内に収まる必要がある。しかし,全てのパスディレイを毎世代・全個体について計算すると計算量が増大する。そこで処理時間の短縮を目的に,図 2 に示すように,ある特定の世代の時にのみ全てのパスでディレイを計算・評価し,それ以外の世代では,特定のパス(遅延が大きいものから n 本:n はパラメータ)についてのみパスディレイの計算・評価を行った。

### (4)低容量化による評価

低消費電力を実現するために,信号遷移率が高いネットの負荷容量(配線容量)を下げる評価関数を新しく考案した。具体的には,信号遷移率が閾値以上のネットの仮想配線長の総和を評価とした。

# (5)消費電力分散度による評価

消費電力の大きなセルを1箇所に配置すると,発熱など

†立命館大学 VLSI センター ‡立命館大学 理工学部 {yosikawa,terai}@se,ritsumei.ac.jp

## 寺井 秀一<sup>‡</sup> Hidekazu Terai

の弊害を起こす可能性がある。また,1つのセル列(同じ電源ラインで駆動するセル列)に同時にスイッチングする消費電力の大きなセルを配置するとピーク電流が増大する。そこで概略配置では,各部分領域に割り当てたセルの消費電力の総和を求め,その最大値から最小値を引いた値を評価関数とした。また詳細配置では,各セル列の消費電力の総和を求め,その最大値から最小値を引いた値を評価関数とした。

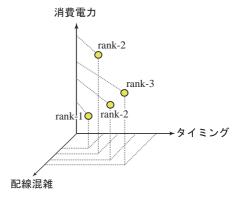

#### 2.2 階層化ペクトルランキング

本手法で提案するような配置手法のような多目的(多評価)最適化問題において,各評価関数の線形和を求めて,それを評価にすることがまず考えられる。しかし,多点探索を行う GA の特性を考慮すれば,線形和によるスカラー化手法で探索を行うより,図2に示すようなベクトルデータによるランキングを用いてパレート最適解の集合を求める方が,より広い解空間を探索することができる。しかし,単純にベクトルデータによるランキングを用いると,評価の優先度を考慮することが出来ない。そこで,評価の優先度に応じて階層的にランキングを行うことでこの問題を回避する。具体的には,まず仮想配線長の概略値による評価・低容量化による評価・タイミング制約による評価を用いてランク付けを行い,ランクが同じ個体に対しては,残りの2つの評価(配線混雑・消費電力分散)で再ランク付けを行った。

図1 パス評価のタイミング

図2 ベクトルデータによるランキング

# 4. 並列計算機への実装

#### 4.1 並列処理方式

セル配置における並列化を考えた場合,各プロセッサ (PU)にLSIの部分領域を割り当て,各PUが割り当てられた部分領域の配置処理を順次行っていく並列化が考えられる。しかし,本稿で提案する概略配置では,最も処理時間を要するのは1回目の分割であり(遺伝子長が最も長い),このような処理時間を多く要する初期の段階において,部分領域が"十分な数(少なくともPU数)"生成されていないため,各PUに部分領域を割り当てる並列処理方式が有効であるとは言えない。そこで本研究では,GAの全個体をいくつかの部分個体群に分割し,それぞれの部分個体群にPUを割り当てる並列処理方式を採用した。

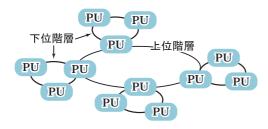

#### 4.2 階層化リングトポロジー

生物学的な棲み分けと分化の現象を土台に,本研究では図3に示すような2段階の階層構造をもつリングトポロジーを新しく考案した。階層化リングトポロジーでは,近傍の部分個体群間(下位のPU間)では個体交換の頻度を高く,遠方の部分個体群間(上位のPU間)での個体交換の頻度は低くした。

# 5. 実験評価・考察

提案手法 (PDP) の有効性を確認するために,セル数 969・ネット数 1089 の  $0.35 \,\mu$  mCMOS 論理データを用いて 商用の EDA ツール (CET) との比較実験を行った。

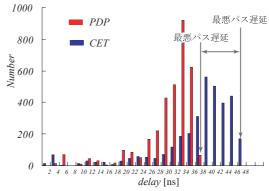

配置結果を表 1 に示す。処理時間以外全ての配置評価項目でCETに比べてPDPの方が良好な結果となった。まず,消費電力に関して,高遷移率ネットの配線容量を削減することで,レイアウト設計段階で消費電力の削減が可能であることを確認した。次に,タイミング制約に関して最悪パス遅延を 22.5%改善した。各パスの状態を図 4 に示す。

図3 階層化リングトポロジー

図 4 より,最悪パス遅延だけでなく,すべてのパスについて改善したことが読み取れる。今回実験に使用したデータは,0.35 μm であるが,100nm以下の微細プロセスでは,RC に起因する配線遅延は増大するため,提案手法による配線遅延の改善がより顕著に現れると考える。また,並列計算機に実装した結果,12PUで11.2 倍の高速化が可能となった。

### 6. まとめ

本稿では,進化戦略をベースとするパフォーマンスドリプン配置手法を提案し,商用の EDA ツールとの比較実験によりその有効性を確認した。提案した配置手法では,2段階の配置手法をベースに,低容量化による消費電力の削減,発熱・ピーク電流の増加を抑制するための消費電力の分散化,タイミング制約,配線混雑緩和,チップ面積最小化の各評価関数をGAの進化ループの中に組み込むことで,配置性能を向上した。今後の課題としては,配置の段階でクロストークノイズを低減するための制約モデルの検討が挙げられる。

#### 参考文献

- (1) J.Holland: Adaptation in Natural Artificial Systems, Second edition; MIT Press, (1992)

- (2) K.Shahookar, et al, "Genetic beam search for gate matrix placement," IEE-proc.E: Computers and digital Techniques, vol. 141, No. 2, pp. 123-128, (1994).

- (3) H.Esbensen et al, "SAGA: Unification of genetic alg orithm with simulated annealing and its application to macro-cell placement", Proc. IEEE Int. Conf. VLSI Design, (1994).

- (4) L.Jens,"A Parallel genetic Algorithm for Performance- Dri ven VLSI routing,"IEEE Trans. Evolutionary Computation, Vol.1,No.1,pp.29-39(1997)

- (5) 中矢,小出,若林:"適応的遺伝的アルゴリズムに基づくVLSIフロアプランニングの一手法",情報処理学会論文誌,vol.43,No.5,pp.1361-1371(2002)

図4 各パスの状態

表 1 配置結果

|     | 高遷移率ネット配線長    | 最悪パス遅延  | 総配線長           | 消費電力分散度                 | 配線混雑度    | 処理時間     |

|-----|---------------|---------|----------------|-------------------------|----------|----------|

| PDP | $33317~\mu$ m | 34.59ns | $138085~\mu$ m | $40.0\mu\mathrm{W/MHz}$ | 1571grid | 55680sec |

| CET | $37752~\mu$ m | 44.65ns | $154714~\mu$ m | 51.1 μ W/MHz            | 1869grid | 58sec    |

| 改善率 | 11.7%         | 22. 5%  | 10.7%          | 21.7%                   | 15. 9%   | _        |